# Simulation Study of a Novel Algorithm for Digital Relaying Based on FPGA

Renwang He, Dandan Xie, Yuling Zhao, Yibo Yang School of Electrical and Electronic Engineering, East China Jiaotong University, 330013 Nanchang, P. R. China E-mail: freeman2he@126.com

**Abstract.** The paper proposes a new fast Fourier transform (FFT) protection algorithm for digital relaying based on field-programmable gate array (FPGA), constructs detailed models and performs corresponding simulations. Simulation results show that the harmonic components of voltages and currents can be conveniently calculated, and the digital protection functions can be effectively fulfilled with enhanced accuracy and reduced storage requirements.

Keywords: radix-4 FFT; Qua-input/output; digital protection; MATLAB

### 1 Introduction

The power system fault signals contain a large number of harmonics and a DC component[1], it needs to extract necessary information to estimate whether the digital protection should operate. Most of the digital protections need to extract the fundamental signal, and filter the other harmonics to avoid malfunction[2]. Fast Fourier Transform (FFT) algorithm can extract every harmonic without attenuation, guaranteeing the other integer harmonics and the DC component attenuating to zero, but can not eliminate the non-integer harmonics and the capacity for suppressing non-periodic components in low-frequency is poor. The radix-4 decomposition, which divides the input sequence recursively to form four-point sequences, has the advantage that it requires only trivial multiplications in the four-point DFT. This results in the highest throughput decomposition, while requiring non-trivial complex multiplications in the post-butterfly twiddle-factor rotations only. Complex multiplication decrease and the four inputs and outputs parallel processing improves processing speed greatly.

## 2 Fourier digital protection algorithm

When ignore the non-integer periodic components, the voltage and current signals in power system can be expressed in the form of Fourier series,

$$x(t) = \sum_{k=0}^{\infty} X_k \cos(k\omega_1 t + \phi_k). \tag{1}$$

where  $^{k=0}$  expresses the DC component;  $^{\omega_1}$  is the fundamental angular frequency;  $^{X_k}$ ,  $^{\omega_k}$  is the amplitude and phase of the  $^{k'^h}$  harmonic component respectively. Expand expression (1) and accord the orthogonality of the trigonometric

functions in  $[0, T_1]$ , it can be derived:

$$X_{Rk} = X_k \cos \phi_k = \frac{2}{T_1} \int_0^{T_1} x(t) \cos(k\omega_1 t) dt.$$

(2)

$$X_{Ik} = -X_k \sin \phi_k = -\frac{2}{T_1} \int_0^{T_1} x(t) \sin(k\omega_k t) dt$$

(3)

$X_{Rk}$ ,  $X_{Rk}$  are the real and imaginary parts of the  $k^{th}$  harmonic component respectively.  $X_{k}$ ,  $X_{Rk}$ ,  $X_{Rk}$  are analog while X(k),  $X_{R}(k)$ ,  $X_{I}(k)$  are digital. Each cycle samples N points and the integral is approximate to the sum [3].

$$X_{Rk} \approx X_R(k) = \frac{2}{N} \sum_{n=0}^{N-1} x(n) \cos\left(\frac{2\pi}{N} n k\right).$$

(4)

$$X_{Ik} \approx X_{I}(k) = -\frac{2}{N} \sum_{n=0}^{N-1} x(n) \sin\left(\frac{2\pi}{N} nk\right).$$

(5)

where x(n) is the  $n^{th}$  sampled value of x(t).

# 3 Radix-4 FFT algorithm

The sampled power system voltage or current signals are discrete periodic sequences. Their Discrete Fourier Transform (DFT) expressions are:

$$X(k) = \sum_{n=0}^{N-1} x(n)e^{-j\frac{2\pi}{N}nk} = \sum_{n=0}^{N-1} x(n)W_N^{nk}.$$

(6)

where

$$W_N = e^{-j\frac{2\pi}{N}}$$

From (5) and (6), it can be obtained

$$X_{Rk} + jX_{Ik} = X_{R}(k) + jX_{I}(k) = \frac{2}{N} \sum_{n=0}^{N-1} x(n)W_{N}^{nk} = \frac{2}{N}X(k).$$

(7)

Each harmonic needed in digital protection can be calculated by using DFT algorithm.

FFT algorithm is an improvement of the DFT algorithm. This paper mainly introduces the radix-4 FFT algorithm according to the DIF (decimation in frequency) [4].

The sampled points during every cycle are  $N=4^L$ , and expression (7) can be written as:

$$X(k) = \sum_{n_0=0}^{3} \sum_{n_1=0}^{3} \cdots \sum_{n_{L-1}=0}^{3} x(n_{L-1}, n_{L-2}, \cdots n_1, n_0) W_N^{nk}.$$

(8)

where

$$n = \sum_{i=0}^{L-1} n_i 4^i$$

$k = \sum_{i=0}^{L-1} k_i 4^i$   $n_i, k_i = 0,1,2,3$

Expression (8) can be written in matrix form

$$\begin{bmatrix} X_1(0,n_{L-2},\cdots,n_0) \\ X_1(1,n_{L-2},\cdots,n_0) \\ X_1(2,n_{L-2},\cdots,n_0) \\ X_1(3,n_{L-2},\cdots,n_0) \end{bmatrix} = \begin{bmatrix} W_4^0 \ W_4^0 \ W_4^0 \ W_4^1 \ W_4^2 \ W_4^3 \\ W_4^0 \ W_4^2 \ W_4^4 \ W_4^6 \\ W_4^0 \ W_4^3 \ W_4^6 \ W_4^9 \end{bmatrix} \begin{bmatrix} x(0,n_{L-2},\cdots,n_0) \\ x(1,n_{L-2},\cdots,n_0) \\ x(2,n_{L-2},\cdots,n_0) \\ x(3,n_{L-2},\cdots,n_0) \end{bmatrix} = \begin{bmatrix} 1 & 1 & 1 & 1 \\ 1 & -j & -1 & j \\ 1 & -1 & 1 & -1 \\ 1 & j & -1 & -j \end{bmatrix} \begin{bmatrix} x(0,n_{L-2},\cdots,n_0) \\ x(1,n_{L-2},\cdots,n_0) \\ x(2,n_{L-2},\cdots,n_0) \\ x(3,n_{L-2},\cdots,n_0) \end{bmatrix}.$$

The multiplication of -j and j just needs only to exchange the real part with the imaginary and adds the necessary plus or minus sign. Expression (9) shows that the computer storage requirements are greatly reduced and the processing speed is enormously enhanced.

## 4 MATLAB simulations

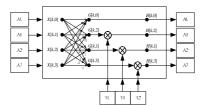

Sample 64 points per cycle. The 64 points will be divided into four groups, paralleled qua-input and qua-output natural order in the same address, the most critical factor in the calculation is to determine twiddle factors and data reordering. The data flow figure of the basic processor, A0, A1, A2, A3 is the four sets of data. T0, T1, T2 are the corresponding twiddle factors in multiplications each four points group. The processing flow is shown in Figure 1. MATLAB simulation results verify the correctness and effectiveness of the proposed algorithm.

Fig. 1. Basic FFT data flow

### 5 Conclusions

In this paper, the 64-point data in four groups have been reordered twice, and both of the input and the output of the qua-input/output radix-4 FFT algorithm are in natural order. All the necessary power system harmonics are employed as information and criterion of the digital protection. MATLAB simulation results show that the proposed algorithm can reduce the computer storage requirements and increase the processing speed of the digital protection system.

# Acknowledgments

The authors would like to thank the Research Fund of East China Jiaotong University which supports the project (09DQ08).

### References

- Babu, P.S., Kumar, S.J.: Accelerated Fourier Algorithm based Digital Multifunction Relay for Transmission Line Protection, Fifteenth National Power Systems Conference, pp. 23-27. Bombay(2008)

- 2. Chuanli Zhang, Yizhuang Huang, Xing-guo Wang, "Application and research of new algorithm for microcomputer-based transformer relaying protection", Relay, 1997.3-27(2), pp. 1-4. Xuchang(1997)

- 3. Jiangang Liu, Tongjing Sun, "Application of Fourier algorithm based on FFT in microcomputer-based relay protection", Relay, 2004, 32(10), pp. 24-26,30. Xuchang (2004)

- 4. Peiqing Cheng, Digital Signal Processing Tutorial, Tsinghua University publication, Beijing (2006)